Special offers from our partners!

Find Replacement BBQ Parts for 20,308 Models. Repair your BBQ today.

App-180

*14: The Universal model QCPU except the Q00UJCPU, Q00UCPU, Q01UCPU, and Q02UCPU.

*15: The range is from 1 to 9 for the Q03UDCPU, Q04UDCPU, and Q06UDHCP whose first 5 digits of serial number is "10012" or earlier.

(Default: 2 Or when setting other than 1 to 9, the register operates as 9).

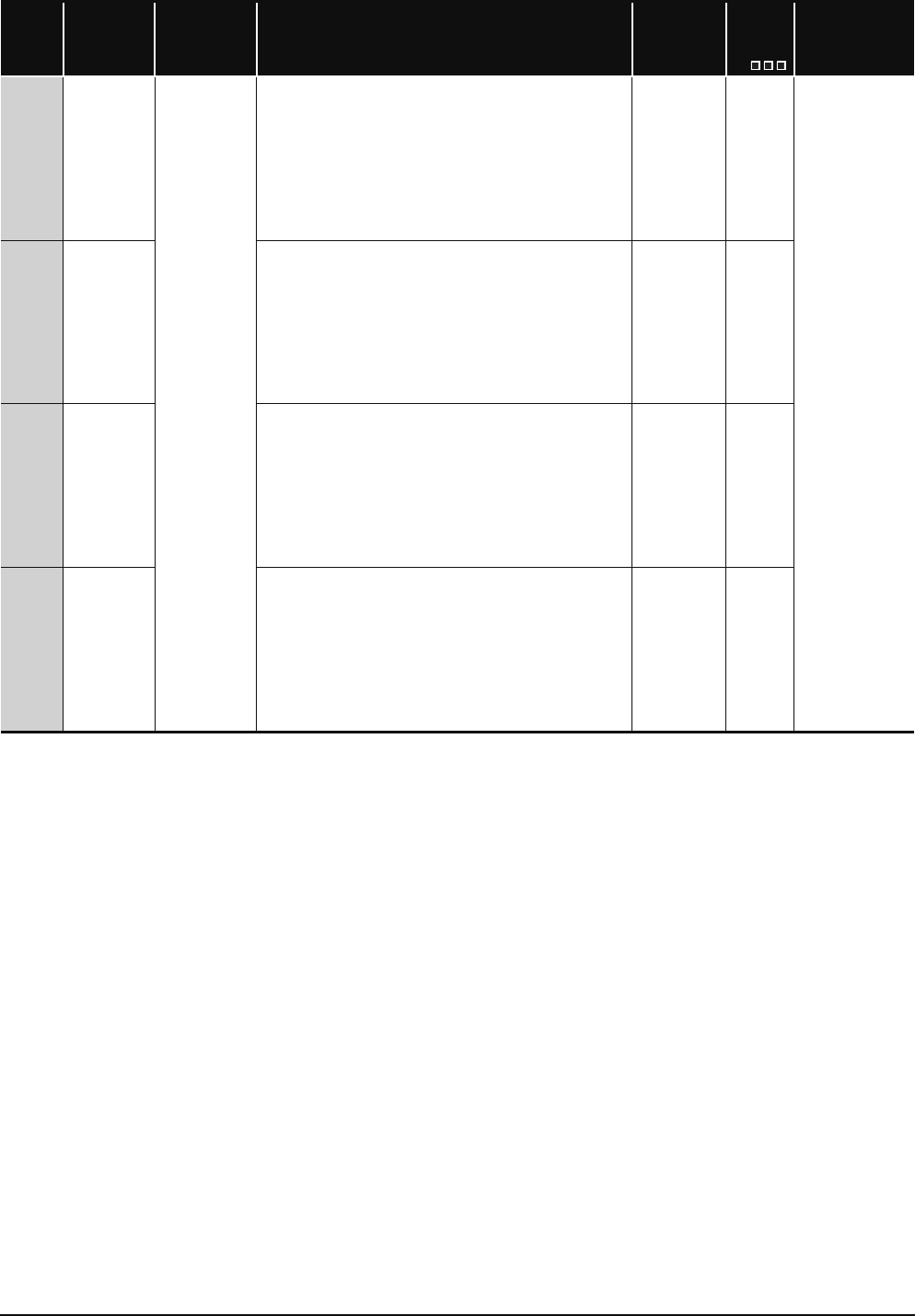

TableApp.4.8 Special register

Number Name Meaning Explanation

Set by

(When Set)

Corres-

ponding

ACPU

D9

Corresponding

CPU

SD796

Maximum

number of

blocks used for

the multiple

CPU high-

speed

transmission

dedicated

instruction

setting (for CPU

No.1)

Maximum number

of blocks range for

dedicated

instructions

Range: 1 to 7

(Default: 2 Or

when setting other

than 1 to 7, the

register operates

as 7).

• Specifies the maximum number of blocks used for the multiple CPU

high-speed transmission dedicated instruction (target CPU=CPU No.1).

When the dedicated instruction of Multiple CPU transmission is

executed to the CPU No.1, and the number of empty blocks of the

dedicated instruction transmission area is less than the setting value of

this register, SM796 is turned ON, which is used as the interlock signal

for consecutive execution of the dedicated instruction of Multiple CPU

transmission.

U (At 1 scan

after RUN)

New

QnU

*14*15

SD797

Maximum

number of

blocks used for

the multiple

CPU high-

speed

transmission

dedicated

instruction

setting (for CPU

No.2)

• Specifies the maximum number of blocks used for the multiple CPU

high-speed transmission dedicated instruction (target CPU=CPU No.2).

When the dedicated instruction of Multiple CPU transmission is

executed to the CPU No.2, and the number of empty blocks of the

dedicated instruction transmission area is less than the setting value of

this register, SM797 is turned ON, which is used as the interlock signal

for consecutive execution of the dedicated instruction of Multiple CPU

transmission.

U (At 1 scan

after RUN)

New

SD798

Maximum

number of

blocks used for

the multiple

CPU high-

speed

transmission

dedicated

instruction

setting (for CPU

No.3)

• Specifies the maximum number of blocks used for the multiple CPU

high-speed transmission dedicated instruction (target CPU=CPU No.3).

When the dedicated instruction of Multiple CPU transmission is

executed to the CPU No.3, and the number of empty blocks of the

dedicated instruction transmission area is less than the setting value of

this register, SM798 is turned ON, which is used as the interlock signal

for consecutive execution of the dedicated instruction of Multiple CPU

transmission.

U (At 1 scan

after RUN)

New

SD799

Maximum

number of

blocks used for

the multiple

CPU high-

speed

transmission

dedicated

instruction

setting (for CPU

No.4)

• Specifies the maximum number of blocks used for the multiple CPU

high-speed transmission dedicated instruction (target CPU=CPU No.4).

When the dedicated instruction of Multiple CPU transmission is

executed to the CPU No.4, and the number of empty blocks of the

dedicated instruction transmission area is less than the setting value of

this register, SM799 is turned ON, which is used as the interlock signal

for consecutive execution of the dedicated instruction of Multiple CPU

transmission.

U (At 1 scan

after RUN)

New